5-9 October 2020, Salt Lake City, UT, USA, University of Utah Conference Center

Conference Theme: "Open-source VLSI Technologies"

Thank you everyone for attending VLSI SoC 2020

The Best Paper Award - Breaking Barriers: Maximizing Array Utilization for Compute In-Memory Fabrics - Brian Crafton

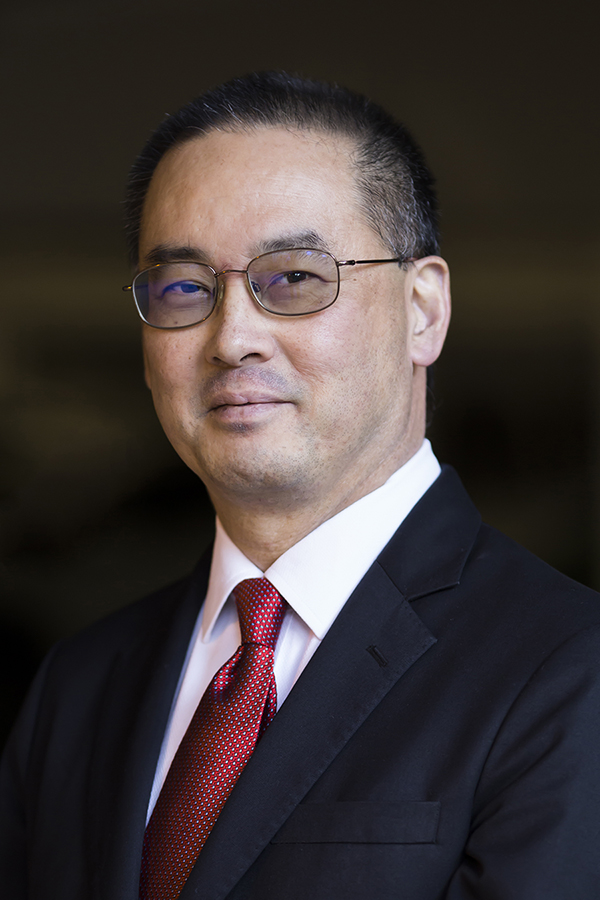

Message from the General Chair

Dear VLSI-SoC 2020 contributors, attendees, and enthusiasts,

Due to the ongoing pandemic of COVID-19, VLSI-SoC 2020 is going to embark on the virtual experience. The main focus of the organizing committee to provide a way to exchange new ideas and promote Open-source Technologies in the most engaging way while accounting for the challenges of having colleagues all over the world. The modalities of the virtual transition will be communicated in due time. VLSI-SoC has always been an exemplary workshop for early scientific dissemination and exchange. As such, we would welcome any advice and recommendations that our community might have to make the first virtual VLSI-SoC 2020 a successful event.

Please feel free to reach out directly to the general chair, Pierre-Emmanuel Gaillardon (pierre-emmanuel.gaillardon@utah.edu) for any ideas.

Best wishes,

Pierre-Emmanuel Gaillardon, on behalf of the VLSI SoC 2020 organizing committee

Important Dates

Full paper submission (Final Extension) : May 11, 2020

Special session proposal: April 27, 2020

Notification of acceptance: June 29, 2020 (Extended)

Camera-ready: August 21, 2020

Ph.D. forum submission: July 24, 2020 (Extended)

Ph.D. forum- Notification of acceptance: August 7, 2020 (extended)

PhD forum Camera-ready Submission: August 21, 2020 (extended)

Keynote Speakers

Edith Beigne

Silicon Research Manager @ Facebook

AR/VR applications: Silicon challenges and Research directions

Augmented reality (AR) is a set of technologies that will fundamentally change the way we interact with our environment. It represents a merging of the physical and the digital worlds into a rich, context-aware, and accessible user interface delivered through a socially acceptable form factor such as eyeglasses. One of the biggest challenges in realizing a comprehensive AR experience is managing power consumption to ensure both adequate battery life and a physically comfortable thermal envelope. This presentation reviews advanced concepts in minimizing power in data transfer across components, leveraging highly efficient accelerators while maintaining programmability, and the potential of emerging nonvolatile memories for low power computing.

Edith Beigné is the Research Director of AR/VR Silicon at Facebook. Her main research interests today are low power digital and mixed-signal circuits and design with emerging technologies. Before that, she was with CEA-LETI, France, where she was the Research Director of Integrated Circuits and System Division. Over the past 20 years, she has been focusing her research on low power and adaptive circuit techniques, exploiting asynchronous design and advanced technology nodes for different applications ranging from high-performance MPSoC to ultra-low-power IoT and, more recently, AR/VR applications. She is part of ISSCC TPC since 2014, chair of the digital circuits sub-committee, and part of the VLSI symposium TPC since 2015. Distinguished Lecturer for the SSCS in 2016/2017, Women-in-Circuits Committee chair, and JSSC Associate Editor since 2018. She visited Stanford University in 2018 to research on emerging technologies and new architectures.

The next step in Computer Architecture - Efficient Machine Learning Architecture

Uri Weiser is a Professor emeritus at the Electrical Engineering department, the Technion IIT and is in the advisory board of numerous startups. He received the bachelor and master degrees in Electrical Engineering from the Technion and Ph.D in CS from the University of Utah, Salt Lake City.

Professor Weiser worked at Intel from 1988 till 2007. At Intel, Weiser initiated the definition of the first Pentium® processor, drove the definition of Intel's MMX™ technology, invented the Trace Cache, co-managed the a new Intel Microprocessor Design Center at Austin, Texas and formed an Advanced Media applications research activity.

Professor Weiser was appointed to Intel Fellow in 1996, in 2002 he became an IEEE Fellow and in 2005 an ACM Fellow. In 2016 Professor Weiser received the IEEE/ACM Eckert-Mauchly Award for “leadership, as well as pioneering industry and academic work in high performance processors and multimedia architectures”. The Eckert-Mauchly award is known as the computer architecture community’s most prestigious award.

Prior to his career at Intel, Professor Weiser worked for the Israeli Department of Defense as a research and system engineer and later with National Semiconductor Design Center in Israel, where he led the design of the NS32532 microprocessor.

Professor Weiser was an Associate Editor of IEEEMicro Magazine and was Associate Editor of Computer Architecture Letters.

Uri Weiser

Emeritus professor @ Technion IIT

Andrew Kahng

Professor @ UC San DiegoOpen-Source EDA: If We Build It, Who Will Come?

The VLSI technology and scaling roadmap has always included Process technology (wrapped as “PDK”), VLSI designs themselves (“System Drivers”), and EDA technology (“Design Technology”). Today, we see an open-source foundry PDK and design enablement, and we see a vibrant open-source hardware ecosystem. But what about open-source EDA? The development of open-source EDA technology cannot be separated from the question, “If we build it, who will come?” Today’s talk will try to provide some thoughts on this question. What is “it”? Who is “we”? Who is “who”? And in what ways will the “who” come to interact with open-source EDA?

Andrew B. Kahng is distinguished professor of CSE and ECE and holder of the endowed chair in high-performance computing at UC San Diego. He was visiting scientist at Cadence (1995-97) and founder/CTO at Blaze DFM (2004-06). He is coauthor of 3 books and over 500 journal and conference papers, holds 34 issued U.S. patents, and is a fellow of ACM and IEEE. He served as general chair of DAC, ISPD and other conferences, and from 2000-2016 as international chair/co-chair of the ITRS Design and System Drivers working groups. Since June 2018 he has served as PI of “OpenROAD” https://theopenroadproject.org/, a $12.4M U.S. DARPA project targeting open-source, autonomous (“no human in the loop”) tools for IC (“RTL-to- GDS”) physical implementation.